在現(xiàn)代集成電路(IC)設(shè)計(jì)中,仿真驗(yàn)證是確保功能正確性和性能優(yōu)化的關(guān)鍵環(huán)節(jié)。隨著設(shè)計(jì)復(fù)雜度的不斷提升,傳統(tǒng)的軟件仿真方法在速度和效率上已難以滿(mǎn)足需求。Aldec公司的硬件仿真系統(tǒng)(HES)通過(guò)硬件加速技術(shù),為IC設(shè)計(jì)提供了高效、可靠的解決方案。本文將探討如何利用HES系統(tǒng)快速實(shí)現(xiàn)各類(lèi)IC設(shè)計(jì)的高級(jí)硬件加速仿真軟件開(kāi)發(fā)。

HES系統(tǒng)基于FPGA或?qū)S糜布脚_(tái),能夠?qū)⒃O(shè)計(jì)映射到硬件中執(zhí)行,從而大幅提升仿真速度。相比純軟件仿真,硬件加速可將仿真時(shí)間從數(shù)周縮短至數(shù)小時(shí)甚至更短。這對(duì)于大規(guī)模SoC(系統(tǒng)級(jí)芯片)或AI加速器設(shè)計(jì)尤為重要,設(shè)計(jì)團(tuán)隊(duì)可以在早期階段快速迭代,驗(yàn)證設(shè)計(jì)邏輯、時(shí)序和功耗。

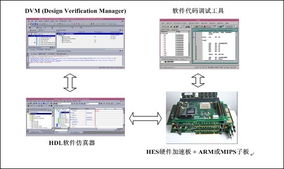

HES系統(tǒng)支持多種設(shè)計(jì)語(yǔ)言和標(biāo)準(zhǔn),如VHDL、Verilog和SystemVerilog,并集成了UVM(通用驗(yàn)證方法學(xué))等驗(yàn)證框架。開(kāi)發(fā)人員可以利用Aldec提供的工具鏈,輕松將現(xiàn)有設(shè)計(jì)代碼編譯并部署到HES平臺(tái)。系統(tǒng)還提供豐富的調(diào)試功能,例如實(shí)時(shí)信號(hào)探針、波形分析和性能監(jiān)控,幫助快速定位設(shè)計(jì)錯(cuò)誤。

在軟件開(kāi)發(fā)方面,Aldec的HES系統(tǒng)提供API和腳本接口,支持自動(dòng)化流程集成。設(shè)計(jì)團(tuán)隊(duì)可以編寫(xiě)自定義腳本,實(shí)現(xiàn)仿真任務(wù)的批量處理、結(jié)果分析和報(bào)告生成。HES可與主流EDA工具(如Cadence、Synopsys)無(wú)縫協(xié)作,構(gòu)建端到端的驗(yàn)證環(huán)境。通過(guò)利用HES的并行處理能力,開(kāi)發(fā)人員能夠優(yōu)化仿真策略,例如分區(qū)仿真和動(dòng)態(tài)負(fù)載均衡,進(jìn)一步提升效率。

實(shí)際應(yīng)用中,HES系統(tǒng)已成功用于處理器、通信芯片和汽車(chē)電子等領(lǐng)域。例如,在5G基帶芯片開(kāi)發(fā)中,HES硬件加速使得協(xié)議棧和射頻模塊的聯(lián)合仿真成為可能,大幅縮短了產(chǎn)品上市時(shí)間。同時(shí),系統(tǒng)支持功耗和熱分析,有助于在設(shè)計(jì)早期識(shí)別潛在問(wèn)題。

Aldec的HES系統(tǒng)通過(guò)硬件加速技術(shù),為IC設(shè)計(jì)提供了快速、可擴(kuò)展的仿真解決方案。結(jié)合靈活的軟件開(kāi)發(fā)工具,設(shè)計(jì)團(tuán)隊(duì)能夠高效實(shí)現(xiàn)復(fù)雜IC的驗(yàn)證目標(biāo),推動(dòng)創(chuàng)新并降低開(kāi)發(fā)風(fēng)險(xiǎn)。隨著AI和物聯(lián)網(wǎng)應(yīng)用的興起,HES系統(tǒng)將繼續(xù)在硬件仿真領(lǐng)域發(fā)揮關(guān)鍵作用。